# Nano-Micro Letters

**REVIEW**

https://doi.org/10.1007/s40820-025-01898-8

Cite as Nano-Micro Lett. (2026) 18:69

Received: 13 May 2025 Accepted: 25 July 2025 © The Author(s) 2025

# Beyond the Silicon Plateau: A Convergence of Novel Materials for Transistor Evolution

Jung Hun Lee<sup>1,3</sup>, Jae Young Kim<sup>2,3</sup>, Hyeon-Ji Lee<sup>3</sup>, Sung-Jin Choi<sup>5</sup>, Yoon Jung Lee<sup>3,4,5</sup> ⊠, Ho Won Jang<sup>3,6</sup> ⊠

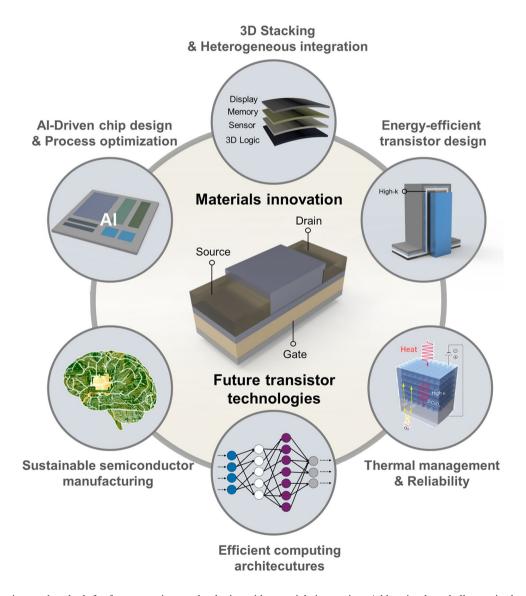

# HIGHLIGHTS

- This review introduces promising semiconductor materials for future transistors, including two-dimensional van der Waals materials, Mott

insulators, halide perovskites, and amorphous oxides, with advantages such as clean interfaces, ultra-thin channels, and defect tolerance.

- These materials, when combined with advanced gate dielectrics and next-generation interconnects, offer synergistic solutions to scaling challenges such as carrier scattering, oxide thickness limitations, and interface degradation.

- The review also discusses reliability concerns including thermal instability and leakage current, and explores future applications in artificial intelligence hardware, in-memory computing, and three-dimensional integration.

ABSTRACT As silicon-based transistors face fundamental scaling limits, the search for breakthrough alternatives has led to innovations in 3D architectures, heterogeneous integration, and sub-3 nm semiconductor body thicknesses. However, the true effectiveness of these advancements lies in the seamless integration of alternative semiconductors tailored for next-generation transistors. In this review, we highlight key advances that enhance both scalability and switching performance by leveraging emerging semiconductor materials.

Among the most promising candidates are 2D van der Waals semiconductors, Mott insulators, and amorphous oxide semiconductors, which offer not only unique electrical properties but also low-power operation and high carrier mobility. Additionally, we explore the synergistic interactions between these novel semiconductors and advanced gate dielectrics, including high-K materials, ferroelectrics, and atomically thin hexagonal boron nitride layers. Beyond introducing these novel material configurations, we address critical challenges such as leakage current and long-term device reliability, which become increasingly crucial as transistors scale down to atomic dimensions. Through concrete examples showcasing the potential of these materials in transistors, we provide key insights into overcoming fundamental obstacles—such as device reliability, scaling down limitations, and extended applications in artificial intelligence—ultimately paving the way for the development of future transistor technologies.

KEYWORDS Modern transistors; Transistor scaling; Alternative semiconductors; 3D integration; Device reliability

Jung Hun Lee, Jae Young Kim, and Hyeon-Ji Lee have contributed equally to this work.

- ☑ Yoon Jung Lee, yoonjung.lee@kookmin.ac.kr; Ho Won Jang, hwjang@snu.ac.kr

- Department of Materials Science and Engineering, Northwestern University, Evanston, IL 60208, USA

- Department of Electrical and Computer Engineering, Texas A&M University, College Station, TX 77845, USA

- Department of Material Science and Engineering, Research Institute of Advanced Materials, Seoul National University, Seoul 08826, Republic of Korea

- Department of Chemistry, Northwestern University, Evanston, IL 60208, USA

- <sup>5</sup> School of Electrical Engineering, Kookmin University, Seoul 02707, South Korea

- Advanced Institute of Convergence Technology, Seoul National University, Suwon 16229, Republic of Korea

Published online: 15 September 2025

### 1 Introduction

69

The continuous evolution of transistor technology has driven significant advancements in the semiconductor industry, revolutionizing the field of ranging from the complementary metal-oxide-semiconductor (CMOS) devices to very-largescale-integration (VLSI) applications [1]. Despite the rapid innovation enabled by advanced transistor technology, the extreme scaling of transistors below the 10 nm gate length and the contacted poly pitch (CPP), which includes both channel length and contact length, has necessitated unprecedented efforts, including achieving ultra-low leakage current [2], sub-1 nm equivalent oxide thickness (EOT) of gate dielectrics [3], and sub-3 nm semiconductor body thickness [4, 5]. Throughout CMOS technology history, research has focused on reducing the body thickness of layers in a transistor [6] alongside shallow dopant implantation in the source-drain regions to prevent active dopant diffusion toward the short channel [7]. However, these approaches have not fundamentally resolved the critical issue posed by short-channel effects (SCEs) in transistors structured with sub-10 nm gate length, resulting in additional challenges, including high contact resistance between semiconductor and source-drain electrodes [8].

To effectively mitigate SCEs in modern transistor technology, several structural advancements have been introduced, including fin field-effect transistors (FinFETs) [9], high-dielectric-constant (K) metal gate (HKMG) [10], and siliconon-insulator (SOI) technology [11]. These innovations have enabled scaling of switching power, reducing operating voltage  $(V_{\rm dd})$  to approximately 0.8 V and achieving subthreshold swing (S.S.) values approaching the thermionic limit (60 mV dec<sup>-1</sup>) [12]. Despite these advancements, significant challenges in transistor scalability have led to the adoption of high-end integration strategies such as 3D monolithic integration [13] or heterogeneous integration [14]. While these integration strategies enhance performance efficiency within a constrained device footprint, they need huge efforts due to the complex circuit designs and processing cost. Rather, these strategies do not fully resolve the intrinsic issue in channel carrier scattering at the semiconductor/gate dielectric interface.

As transistor technology continues to progress, it is crucial to develop fundamental strategies that synergize with high-end integration technologies and structural tuning.

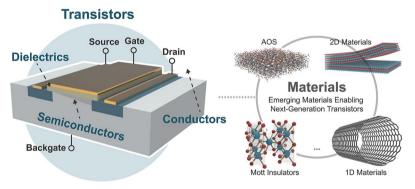

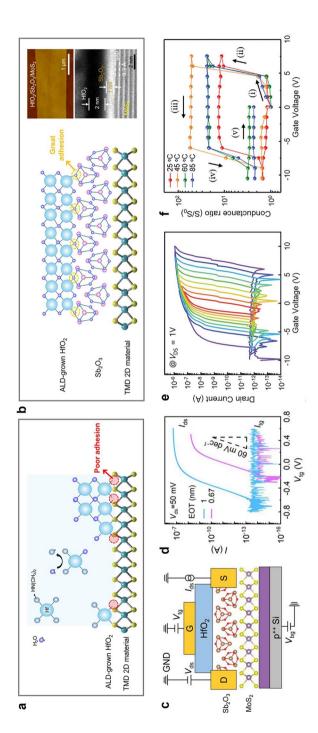

One such strategy is to focus on a microscopic channel perspective to promote scattering-free carrier transport. By prioritizing this approach, we can propose a fundamentally innovative but simple solution to drive further advancements in the semiconductor industry. To enhance the channel carrier motion in semiconductors, we need to study alternative semiconductors that can be replaceable for silicon. Figure 1a shows several new classes of semiconductors along with representative high-*K* dielectrics and ferroelectric materials.

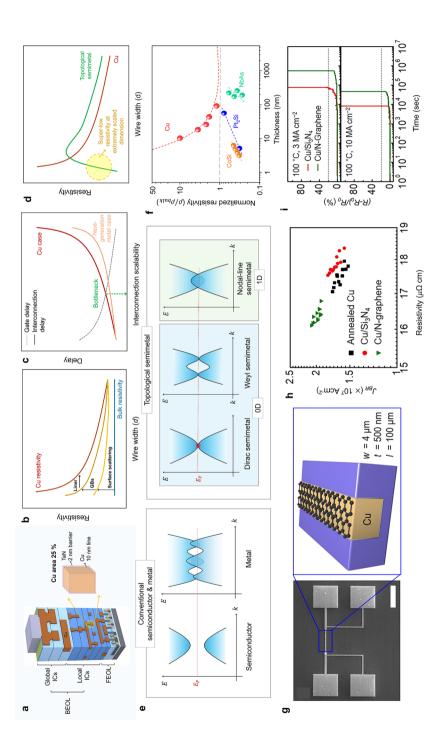

In this review, we suggest several alternative semiconductors that can be promising candidates for future scalable transistors. New classes of semiconductors including two-dimensional (2D) van der Waals (vdW) semiconductors, Mott insulators, halide perovskites, and amorphous oxide semiconductors will be introduced with recently reported publications (Fig. 1b). All these materials have shown their unique characteristics including atomically clean surface, ultra-thin body thickness, femto-scale fast switching by gating-induced electron correlation, high carrier mobility, and intrinsic defect tolerance. These properties have been huge advantages for low-powered and highly scalable transistors. Along with the introduced semiconductors, we will address the synergies of new semiconductors/gate insulators including 2D hexagonal boron nitrides, high-K dielectrics, and ferroelectric layers (Fig. 1c). By effectively alleviating the EOT degradation issue originating from the increased interfacial defect density  $(N_{it})$ , unfavored nucleation behaviors during the metal oxide growth, degraded ferroelectricity, we can confirm the collaborative usage of dielectrics with new classes of semiconductors. Besides, we will address new metals that can replace interconnects in the back-end-of-line (BEOL). By mitigating the electron scattering on the extremely scaled BEOL region thanks to their unconventional conduction mechanism, several topological semimetals will be introduced (Fig. 1d).

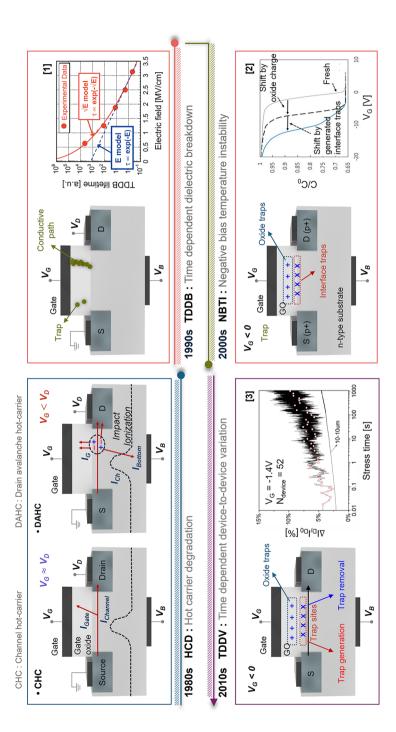

Beyond examining performance innovations in individual transistors, additional concerns are addressed with solutions in Perspectives part. In this part, we care about the device stability issues including thermal instability, leakage current, and long-term degradation—critical concerns in aggressively scaled devices. Additionally, we suggest outlooks for practical application of new materials in modern transistor technologies, in which 3D integration, low-powered

Nano-Micro Lett. (2026) 18:69 Page 3 of 59 69

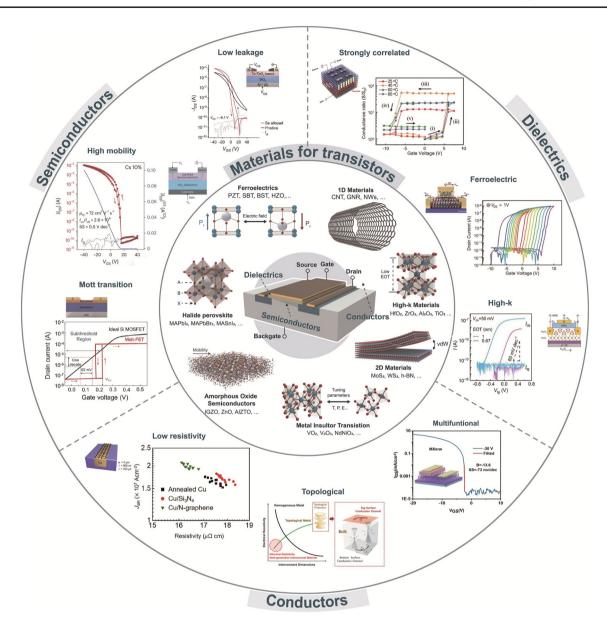

Fig. 1 Material properties employed in transistors and their corresponding applications. a The materials are allocated to specific components of the transistor, namely b semiconductors, c dielectrics, and d conductors. Transistors constructed on the basis of these material properties exhibit superior performance and multi-functionality. Reproduced with permission [15], Copyright 2024, Wiley–VCH GmbH. Reproduced with permission [16]. CC BY 4.0. Reproduced with permission [18]. Copyright 2022, Wiley–VCH GmbH. Reproduced with permission [19]. Copyright 2022, Wiley–VCH GmbH. Reproduced with permission [20]. Copyright 2023, Springer Nature. Reproduced with permission [21]. Copyright 2022, The Author(s). Reproduced with permission [23]. Copyright 2021, Nature Publishing Group

devices, and further commercialization toward AI hardware have been necessitated. This review aims to provide material insights relevant to modern transistor technologies, along-side deep understanding the key roles of future materials in a transistor configuration and proposing importance of combined tuning among materials, structures, and systems.

# 2 Evolution of Transistor Technology

The advancement of transistor technology has been the foundation of the semiconductor industry, driving continuous innovation and exponential growth over the past decades (Fig. 2). The first breakthrough occurred in 1947 with the

69 Page 4 of 59 Nano-Micro Lett. (2026) 18:69

Fig. 2 Trends and future perspectives in transistor structures and materials. The progression of transistor technology, initiated in 1947, followed a scaling trend consistent with Moore's law. While this trend shifted to 3D architectures in the 2000s, scaling challenges prompted the introduction of innovations in materials, operating principles, structures, and systems to further reduce node dimensions beyond traditional scaling limits

development of the point-contact transistor was developed at Bell Labs, followed by the invention of the bipolar junction transistor (BJT) in 1948, establishing the groundwork for modern semiconductor technology [24]. In 1959, the development of the metal-oxide-semiconductor field-effect transistor (MOSFET) enabled significant scalability and integration. Subsequently, in 1963, the introduction of CMOS technology paved the way for large-scale integration (LSI) [25]. These innovations culminated in the release of the world's first commercial microprocessor, Intel 4004, in 1971, marking a milestone in modern semiconductor technology [26]. In 1965, Gordon Moore, co-founder of Intel, formulated Moore's law, predicting that the number of transistors in an integrated circuit would double every 18–24 months. This empirical observation was revised in 1975 to a doubling every two years and became the guiding principle for the semiconductor industry. Since 1993, major semiconductor companies have collaboratively developed the International Technology Roadmap for Semiconductors (ITRS), ensuring the continued progress of Moore's law and industry's technological advancements [27]. However, as transistor dimensions shrank below 100 nm, SCEs have become increasingly problematic, posing fundamental limits to traditional planar MOSFET scaling. In the sub-10 nm regime, quantum mechanical tunneling effects cause excessive leakage currents, leading to reduced on-state current  $(I_{on})$ , increased offstate current  $(I_{\text{off}})$ , and significant power consumption issues. To address these limitations, the semiconductor industry adopted HKMG technology and introduced FinFET architecture in 2011 [28]. FinFETs, with their three-dimensional gate structure, enhanced electrostatic control over the channel, effectively suppressing leakage currents and improving transistor performance. The gate-all-around (GAA) transistor further advanced transistor design by providing even more precise current control, while 3D NAND flash memory introduced high-density storage capabilities. These 3D integrated structures have minimized interconnect delays and improved power efficiency, playing a crucial role in AI and high-performance computing (HPC) applications [29].

While these advancements have successfully extended the limits of transistor scaling, sustaining Moore's law has become increasingly challenging due to fundamental physical and economic constraints. Maintaining Moore's law now requires more than just conventional transistor scaling, as two major obstacles in the form of technological limitations and economic constraints threaten its sustainability. From a technological standpoint, extreme miniaturization below 10 nm leads to quantum tunneling effects, where electrons penetrate the gate oxide, increasing leakage currents and degrading device performance. Furthermore, contact resistance at the source and drain terminals rises as the channel thickness approaches atomic scales, reducing  $I_{\rm on}$  and overall transistor efficiency. Additionally, heat dissipation in advanced 3D stacked architecture has become a major bottleneck, necessitating innovative thermal management solutions. From an economic perspective, the cost-effectiveness of transistor scaling has significantly declined. Since the 65 nm node in 2006, the cost-benefit ratio of reducing transistor size has diminished. The transition to 22 nm and beyond has required extreme ultraviolet lithography (EUV), an advanced patterning technology that has substantially increased fabrication costs. The semiconductor industry has consolidated around a few dominant players, including Intel, TSMC, Samsung, and GlobalFoundries, as the capital-intensive nature of developing cutting-edge nodes has become a barrier to entry. To address these challenges, the semiconductor industry is shifting focus from pure transistor density scaling to system-level performance optimization through novel materials and 3D integration techniques. Heterogeneous semiconductors have gained attention as potential replacements for traditional siliconbased transistors. 2D materials such as MoS<sub>2</sub>, WS<sub>2</sub>, Mott insulators, HPs, and AOSs exhibit promising properties, including high carrier mobility, atomically thin channels, and defect tolerance, making them strong candidates for next-generation transistors. In parallel, the introduction of high-K dielectrics and ferroelectric gate insulators, such as hBN, HfO<sub>2</sub>, and ferroelectric layers, has aimed to reduce the EOT while mitigating interface defect density. Moreover, the transition from planar to 3D monolithic integration is revolutionizing semiconductor architecture. Through-silicon vias (TSV) and compute-in-memory (CIM) technologies are being explored to enhance energy efficiency and reduce data transfer latency, which is particularly crucial for AI-driven workloads and next-generation computing paradigms. The semiconductor industry is continuously exploring new materials, device architectures, and integration methods to overcome the physical limits of Moore's law. As the industry moves beyond conventional scaling-based transistor improvements, the future of semiconductors will be shaped by heterogeneous integration, 3D stacking, and energy-efficient computing systems.

# 3 Challenges in FET Scaling Technology

#### 3.1 Importance of Low-Power Switching

69

For nearly two decades since the 1980s, the semiconductor industry predominantly adopted a standard  $V_{\rm dd}$  of 5 V for digital circuit designs. This was primarily due to the widespread use of bipolar transistor-based digital integrated circuits (ICs) [30]. Even after CMOS technology became the standard architecture for ICs, logic threshold levels remained unchanged to ensure compatibility with existing bipolar logic circuits. However, significant advancements in transistor geometry since the 2000s, particularly as channel lengths shrank below 90 nm [31], enabled the reduction of  $V_{\rm dd}$  to sub-1 V levels. This voltage scaling has led to substantial reductions in power consumption during CMOS operation. Power consumption  $(P_{\rm sw})$  scales with the square of the supply voltage  $(V_{\rm dd})$  as followed Eq. 1, so reducing  $V_{\rm dd}$  by a factor of 5 lowers  $P_{\rm sw}$  by 25 times—driving advances in transistor scaling.

$$P_{\rm sw} = \alpha C_{\rm L} V_{\rm dd}^2 f \tag{1}$$

where  $\alpha$  represents the activation coefficient during switching,  $C_{\rm L}$  is the load capacitance, and f is the clock frequency. This dramatic improvement in power efficiency has driven the acceleration of transistor scaling technology. While device miniaturization efforts since the 2000s have focused on reducing  $P_{\rm sw}$ , further improvements in switching efficiency require continued voltage scaling. The 2024 IRDS roadmap, for example, projects that  $V_{\rm dd}$  will be reduced to below 0.7 V by 2028 [32]. Achieving this target necessitates the development of transistors with low S.S., approaching the fundamental thermal limit of 60 mV dec<sup>-1</sup>, and a small threshold voltage (Vth).

To better understand these critical parameters, we need to examine the physical meaning of S.S. and Vth, along with strategies for minimizing them—particularly in the context of the most widely used transistor in the semiconductor industry: MOSFET. The relationship governing S.S. during transistor switching is given by: For the future target, the most foundational transistor should ultimately have low

S.S.

$$(\text{mVdec}^{-1}) = 60 \text{ mV} \left( 1 + \frac{C_{\text{dep}}}{C_{\text{ox}}} \right)$$

(2)

where  $C_{\rm dep}$  and  $C_{\rm ox}$  represent the depletion layer capacitance and gate dielectric capacitance, respectively. To achieve low S.S., parasitic charges must be minimized and high-quality semiconductor/dielectric interfaces ensured to prevent

charge scattering [33]. However, high switching speeds also require aggressive channel scaling, especially narrowing the source—drain gap, beyond just optimizing channel materials.

Another crucial parameter in MOSFET operation is the *V*th, which defines the transition from weak to strong inversion in the channel. In an *n* type MOSFET (nMOSFET), applying a positive gate voltage induces band bending at the semiconductor/dielectric interface, leading to channel inversion. The key factors influencing *V*th are described by:

$$V \operatorname{th}(V) = V_{\mathrm{FB}} + \frac{\sqrt{4Q_{\mathrm{dm}}qN_{a}\varphi_{\mathrm{B}}}}{C_{\mathrm{ox}}}$$

(3)

where  $V_{\rm FB}$  is the flat-band voltage,  $Q_{\rm dm}$  is the charge density in the semiconductor,  $N_a$  is the doping concentration of the silicon substrate,  $\varphi_{\rm B}$  is the semiconductor bulk potential, and  $C_{ox}$  is the gate dielectric capacitance. When increasing gate voltage, severe downward band bending is caused at the semiconductor surface. Researchers have explored several strategies to lower Vth, including increasing  $C_{ox}$  with high-K gate dielectrics, reducing  $N_a$ , and tuning the flatband voltage  $(V_{FB})$  through alternative gate metals. Among these, the combined use of high-K dielectrics and lightly doped substrates has emerged as a widely adopted solution. A notable example is TSMC's demonstration of a standard nMOSFET with a Vth of 0.847 V [33] using a lightly doped p-type silicon substrate, illustrating the effectiveness of this approach in supporting low-voltage, energy-efficient transistor operation.

#### 3.2 Trend of Transistor Scaling

For low S.S. and Vth value, therefore, charge scattering which interferes with the velocity of charge carriers in channel—must be alleviated. However, it is difficult to control the interfacial defects at gate oxide/semiconductor interface and within semiconductor grain boundaries or imperfections without altering the channel geometry. With the revolution of 3D transistor structure starting from FinFET, GAA FET [34, 35], to nanosheet FET [36, 37], the 3 nm gate node technology has been successfully tried and commercialized with the 3D device structure [38]. Although this trend has accomplished a lot of technological advancement in semiconductor field, several challenges remain the mechanical instability from the etching process to form suspended channel [39], channel strain caused by the vertical stress [40, 41], large parasitic capacitance from the 3D structure [42, 43], and the difficulty in achieving a minimum fin width constrained to 4 nm [44]. To move beyond the 3-nm gate-scaled FET, we must conceive next-generation silicon materials that have enough charge mobility at the sub-1 nm thickness. Along with this necessity for new high-mobility semiconducting materials, the high off-current and the resulting low on/off current ratio originally stemmed from the SCE in a highly scalable device should be resolved. For that, we need pertinent hole concentration along with the rich electron concentration, by balancing electron and hole concentration for the low off-current.

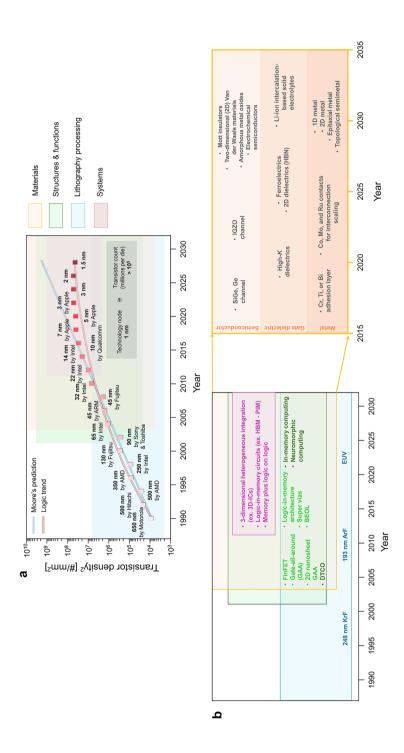

Even though the power-performance-area (PPA), where it has a trade-off relationship among them, could be improved by the reduced gate node width, much more PPA can be further enhanced using silicon alternatives such as 2D transition metal dichalcogenides (TMDs) or 1D carbon nanotube (CNTs) (Fig. 3a). With these replacements, several logic-level issues have been handled. For example, parasitic capacitance can be alleviated by the application of 2D and 1D materials (Fig. 3b). Given that parasitic capacitance is a key obstacle that impedes the speed and energy efficiency of the aggressively scaled silicon transistors due to higher contact area and reduced oxide body thickness, accounting for over 70% of the total capacitance [45], these lowdimensional semiconductors are advantageous to addressing the power issues. Especially in scaled transistors, trapping sites at dense interfaces—one of the main causes of parasitic capacitance—can be alleviated by the van der Waals gap at 2D material surfaces and by the ballistic transport along the surface of CNTs. Therefore, low-dimensional materials are promising candidates for minimizing parasitic capacitance.

According to the 2023 IRDS roadmap [32], 3D VLSI configured with vertical CFET is targeted for implementation by 2034. As this 3D stacking trend continues, the demand for utilizing 2D materials as channel materials in specialty transistor adds-on is expected to increase significantly. In addition, to prevent performance degradation of the lower FET during device processing, the processing temperature of the upper FET must be limited to below 400 °C. By employing thermally robust 2D materials as the channel material for the lower FET, the thermal budget for the upper FET process can be effectively extended. Along with the material suitability for vertical CFET, it is possible to approach the fundamental limit of S.S., which is 60 mV dec<sup>-1</sup> under room temperature, when applying 2D materials (Fig. 3c). It is because the charge mobility is dramatically enhanced compared to the typical silicon. Specifically, the mobility of monolayer TMD 2D and CNT is approximately 10 and 100 times higher than that of silicon, respectively, when compared at the same thickness scale of around 1 nm [48, 50] (Fig. 3d).

Along with this enhanced mobility, the atomically flat and defect-free surfaces of 2D van der Waals semiconductors—free of dangling bonds—facilitate the formation of clean and trap-free interfaces with compatible 2D dielectric materials such as hBN or layered oxides [46, 47]. While such vdW interfaces offer significant advantages in suppressing interface scattering and enabling super low depletion capacitance  $(C_{\rm dep})$ , it should also be noted that additional interface engineering is essential when integrating conventional 3D high-K dielectrics like  ${\rm Al_2O_3}$  or  ${\rm HfO_2}$  due to their intrinsic dangling bonds [48]. Through the use of these highly conductive yet defect-free materials with sub-nanometer thicknesses, substantial progress has been made in realizing low-power transistor switching and aggressive electrostatic scaling.

Although there are a lot of advantages in scaling when using 2D and 1D materials in the semiconductor channel of a transistor, it has still many obstacles to apply those in thin-film transistors (TFTs) display application in terms of difficulties in large-scale uniform coating [49], and alignment issue with metal electrodes [50]. Furthermore, considering the values of intrinsic delay time compared between logic and thin TFTs for display (Table 1), more prolonged intrinsic delay time in TFT applications than that in logic applications alludes that relatively strong gate capacitance and contact resistance between semiconductor and metal should be more carefully controlled in the case of low-dimensional semiconductor devices.

# 3.3 Scaling Limitation and Strategies Based on New Materials

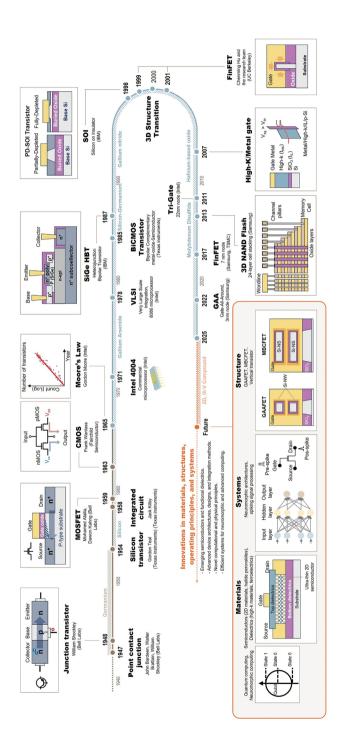

Although Moore's law has long served as a guiding principle for transistor scaling, a growing gap between Moore's predictions and actual trends in logic device scaling has highlighted its limitations in recent decades (Fig. 4a). Since 2010, a critical criterion has emerged, distinguishing between actual transistor sizes and virtual scaling predictions. This shift spurred a paradigm change, addressing transistor scaling through advancements in materials, device functions, fabrication processes, and system evolution. These four key domains have recently led to distinct trajectories within the semiconductor technology landscape (Fig. 4b). Developing diverse

69 Page 8 of 59 Nano-Micro Lett. (2026) 18:69

Fig. 3 Trends of transistor scaling using beyond-silicon materials in recent semiconductor technologies. a Evolution of semiconductor device architecture, progressing from 3D integration to materials beyond silicon. b Conceptual schematic representation of advanced transistor scaling techniques, illustrating the decreasing parasitic capacitance as the years passed. c S.S. trends depending on the gate length in two representative FET types: FinFET and 2D FET [51]. d Exploration of alternative materials for future transistors, such as CNT and 2D TMDs, highlighting their theoretical and experimental performance [52–58]

Table 1 Summary of recent studies about intrinsic time delay of low-dimensional TFTs and logics

| Device type          | CNT TFT | WS <sub>2</sub> TFT | WSe <sub>2</sub> TFT | MoS <sub>2</sub> TFT | CNT logic | WS <sub>2</sub> logic | WSe <sub>2</sub> logic | MoS <sub>2</sub> logic |

|----------------------|---------|---------------------|----------------------|----------------------|-----------|-----------------------|------------------------|------------------------|

| Intrinsic time delay | 281 ps  | 30.7 ps             | 66 ps                | 0.276 ps             | 16 ps     | 0.118 ps              | 8.96 ns                | 6.8 ns                 |

| References           | [59]    | [60]                | [61]                 | [62]                 | [63]      | [64]                  | [65]                   | [66]                   |

solutions beyond nanopatterning technologies has become increasingly important for the future of transistors, particularly due to the limitation of EUV lithography. Despite notable progress, including successful production of 3 nm chips using EUV lithography by Samsung, TSMC, and Intel, several challenges have emerged in terms of the inefficiency of multi-patterning processes [67, 68] and environmental impact of EUV [69]. Consequently, relying solely on next-generation

patterning technologies beyond EUV light sources is not the most effective strategy for continuing device scaling. Instead, researchers are exploring versatile approaches that leverage advancements across the four domains.

In addition to research and development (R&D) revolutions of nanopatterning technologies, new system algorithms and computing functionalities are increasingly integrated into transistor-based hardware. Examples include

Nano-Micro Lett. (2026) 18:69 Page 9 of 59 69

Fig. 4 Scaling limitations of recent FETs. a Transistor density trends over the past 35 years and projections for the next 5 years, highlighting the discrepancy between Moore's prediction and the actual logic scaling trend [104, 105]. Each channel length and the fabrication company is denoted at each trend. A scaling criterion dividing actual transistor device size to virtual transistor size according to Moore's predictions has emerged around 2010. b Evolution of materials [15, 18, 77, 79, 84] for recent transistors device structures [36, 72, 106, 107] and functions [33, 108, 109], lithography processes [110], and systems [72, 111, 112] over the past 40 years. Yellow, green, blue, and red regions represent trends in semiconductor materials, structures and functions, lithography, and system advancements, respectively. Among the several factors to influence scalability, detailed materials trend for metal contacts, gate dielectrics, and semiconductor layers are summarized from 2015 to 2035

69 Page 10 of 59 Nano-Micro Lett. (2026) 18:69

3D heterogeneous integrated architecture [70, 71], logicin-memory circuits [72, 73], and memory plus logic on logic device systems [74, 75]. These innovations have enabled the proposal and validation of new computing paradigms, demonstrating compatibility with other systems and enhancing overall performances. Additionally, a new methodology for time-to-market process—technology co-optimization (DTCO) [76]—has emerged by various semiconductor industries. By introducing one of methods to increase PPA, meaningful circulation between processing and marketing has been enabled. While system-level developments are promising, critical trends in FET technology between 2015 and 2035 have been highlighted by the evolution of critical components such as metal contacts, gate dielectrics, and semiconductor layers. This trend underscores the increasingly complex demands of nextgeneration devices, which extend beyond simple tuning using only semiconducting material.

For the semiconductor layers, transistor devices have been applied by SiGe or Ge [77, 78], indium-gallium-zinc oxide (IGZO) [79, 80], Mott insulators [15, 18], 2D vdW materials [81, 82], HPs [83, 84], and various amorphous metal oxides [17, 85]. For the gate dielectric layers, key materials include high-K dielectrics [86], ferroelectrics [80], 2D dielectrics like hBN [87, 88], and lithium (Li)-ion intercalated solid electrolytes [89, 90]. Meanwhile, molybdenum (Mo) [91], bismuth (Bi) [92, 93], and antimony (Sb) [94–96] have been adopted as an adhesion layer beneath Au or Pt source/drain electrodes to achieve ohmic contact at metal/semiconductor junctions. Additionally, emerging materials such as one-dimensional (1D) metals [97, 98], 2D metal [99–101], or Weyl semimetals (WSMs) [102, 103] are being investigated as an alternative gate material to reduce resistivity.

Ultimately, it is critical to understand how to apply these materials effectively to different transistor configurations. In the following sections, we will comprehensively categorize and discuss the suitability of each material for three key components: semiconductors, gate dielectrics, and metal contacts. We will also analyze their impact on transistor performance and their specific functionalities.

# **4 Next-Generation Semiconductors**

#### 4.1 2D vdW Semiconductors

The synthesis of 2D vdW semiconductors plays a pivotal role in optimizing their structural, electronic, and interfacial properties for high-performance transistor applications. Various synthesis strategies, categorized into bottom-up and top-down approaches, offer distinct advantages depending on the specific requirements of material quality, scalability, and device integration [113].

Bottom-up synthesis methods enable precise control over the atomic structure and crystallinity of 2D materials, making them particularly suitable for high-performance electronic and optoelectronic applications. Chemical vapor deposition (CVD) [113-115] and metal-organic chemical vapor deposition (MOCVD) [116–118] are widely employed techniques for the synthesis of high-quality monolayer and few-layer 2D films. These methods rely on the precisely controlled reaction of vapor-phase precursors under a defined temperature and pressure regime, enabling layer-by-layer growth with exceptional crystallinity and uniformity. The resulting 2D nanosheets exhibit excellent electronic properties, including high carrier mobility and minimal defect density, making them ideal candidates for next-generation transistors. While these methods have enabled the synthesis of wafer-scale 2D films with lateral dimensions extending up to 2-4 inches [119-121], several challenges persist in achieving industrial scalability. Maintaining uniform thickness and crystallinity across large areas remains a critical issue due to variations in precursor flux, thermal gradients, and substrate-induced strain, which can lead to structural inhomogeneities and defect formation at grain boundaries. Addressing these limitations is imperative for the successful integration of 2D materials into scalable electronic and optoelectronic technologies.

Epitaxial growth techniques further refine the bottom-up synthesis of 2D semiconductors by enabling the deposition of atomically precise layers with well-defined crystallographic orientations. Molecular beam epitaxy (MBE) [122–125] utilizes ultra-high-vacuum conditions to direct atomic or molecular beams onto a substrate, allowing for the formation of monolayers or few-layer structures with extreme purity and controlled thickness. This method is particularly advantageous for fundamental studies and

high-performance electronic applications where defects must be minimized. van der Waals epitaxy (vdWE) extends the capabilities of epitaxial growth by leveraging weak van der Waals interactions to enable the synthesis of 2D materials on substrates with lattice mismatches. Unlike conventional epitaxy, which relies on strict lattice registry, vdWE permits the growth of heterostructures with minimal interfacial strain, thereby expanding the range of compatible substrate choices. Nevertheless, similar to CVD and MBE, epitaxial growth techniques face limitations in large-area scalability and are primarily employed for specialized applications where material quality takes precedence over throughput.

For applications requiring high-quality bulk 2D materials, chemical vapor transport (CVT) [126, 127] and flux growth [128] methods provide an effective means of synthesizing pristine crystals that can be subsequently exfoliated into thin layers. In CVT, volatile transport agents, such as halogens, facilitate the vapor-phase migration of precursor species, enabling the controlled crystallization of high-purity bulk materials. This method is widely utilized for the synthesis of layered 2D semiconductors with well-defined stoichiometry and structural integrity. Flux growth, on the other hand, involves dissolving precursor materials in a hightemperature solvent, whereupon controlled cooling induces crystal precipitation. This technique enables the synthesis of large, high-quality single crystals with minimal structural defects, making them particularly valuable for fundamental studies and device fabrication requiring bulk material integrity. Although CVT and flux growth yield high-purity bulk crystals, their direct applicability to wafer-scale integration remains limited. Mechanical exfoliation (ME), while effective for obtaining high-quality monolayers and fewlayer flakes, is inherently restricted in scalability. In contrast, liquid-phase exfoliation (LPE) [129-132] enables the production of solution-processable 2D inks, facilitating the fabrication of large-area thin films through deposition techniques such as spin coating, printing, and solution shearing. This makes LPE-derived films particularly advantageous for scalable transistor applications and flexible electronics. Consequently, CVT- and flux-grown bulk crystals serve as essential precursors for solution-processing techniques, bridging the gap between high-quality material synthesis and large-area device fabrication.

The synthesis of 2D van der Waals semiconductors via bottom-up approaches provides a versatile pathway for tailoring material properties to enhance transistor performance.

While methods such as CVD, MOCVD, and epitaxy enable precise structural control, their scalability remains a challenge for industrial-scale integration. Bulk crystal growth techniques, including CVT and flux growth, offer an alternative route to high-quality layered materials but require additional processing for thin-film applications. Representative studies highlighting wafer-scale growth techniques and fabrication methods of 2D materials [133], including chemical vapor deposition [134, 135], metal-organic CVD (MOCVD) [136], atomic layer deposition (ALD) [137], epitaxial/hypotaxial growth [138, 139], and printing methods approaches [140, 141], serve as valuable resources toward both foundational principles and recent advancements relevant to the scalable integration of 2D semiconductors. The continued development of scalable, high-purity synthesis strategies remains essential for the widespread adoption of 2D materials in next-generation nanoelectronic devices.

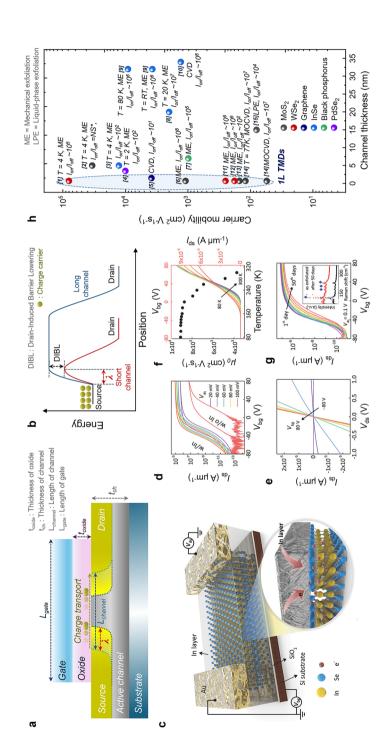

2D vdW semiconductors have emerged as transformative materials for next-generation transistor technologies, offering unique advantages over conventional bulk semiconductors in terms of electrostatic control, dimensional scaling, and charge transport efficiency. The layered structure of vdW materials enables the realization of an atomically thin film at the monolayer limit ( $t_{channel} < 1$  nm) without the formation of surface dangling bonds, thus minimizing surface roughness scattering and suppressing defect-induced trap states. These intrinsic properties allow 2D materials to effectively mitigate short-channel effects (SCEs), which pose a significant challenge in the aggressive downscaling of conventional FETs. In traditional semiconductor FETs (Fig. 5a), as the channel length ( $L_{\text{channel}}$ ) decreases to the nanometer scale, the electrostatic control exerted by the gate becomes increasingly compromised due to the intensified electrostatic coupling between the source and drain electrodes. This results in pronounced SCEs, including drain-induced barrier lowering (DIBL), Vth roll-off, and an increase in S.S.. These effects collectively degrade the transistor's switching behavior, leading to excessive offstate leakage currents, reduced  $I_{\rm on}/I_{\rm off}$  ratios, and unpredictable electrical characteristics, ultimately undermining device reliability and energy efficiency. In contrast, 2D vdW semiconductors inherently mitigate these SCEs due to their atomically thin channel geometry, which significantly enhances electrostatic gate control. The ultra-thin body of 2D materials ensures that the entire channel remains within the gate's electrostatic influence, effectively suppressing

69 Page 12 of 59 Nano-Micro Lett. (2026) 18:69

sulation) measured under varying drain-source voltages ( $V_{ds}$ ), compared with a device without In encapsulation at  $V_{ds} = 0.1 \text{ V}$  [144]. e Output characteristics of the InSe FET (32 nm In encapsulation), demonstrating encapsulation) at different back-gate voltages ( $V_{bg}$ ) with 20 V increments [144]. f Temperature-dependent transfer characteristics of the InSe FET (32 nm In encapsulation), demonstrating carrier mobility trends as a function of temperature. g Stability assessment of the InSe FET (32 nm In encapsulation) over time, showcasing the evolution of transfer characteristics, Raman Fig. 5 2D vdW semiconductors. a Schematic representation of FETs at the extreme scale, depicting critical structural parameters for charge carrier transport. b Energy band diagram illustrating the long-channel and short-channel configurations of a transistor, highlighting DIBL and characteristic screening length (λ). c Schematic of a back-gate InSe FET device, encapsulated with an indium (In) layer to protect and dope the surface. The inset provides details of the SCTD process [144]. d Transfer characteristics of a layered InSe FET (32 nm In encapspectra, carrier mobility, and hysteresis loop window size over 50 days [144]. h Carrier mobility as a function of channel thickness for two-dimensional transistors based on ME [136, 144, 151–158], liquid-phase exfoliation [141], CVD [159], and MOCVD [160] methods. NS\* not specified. Reproduced with permission from [144]. Copyright 2018, Wiley

charge-sharing effects from the drain and minimizing the depletion region encroachment that typically exacerbates DIBL (Fig. 5b). This strong electrostatic confinement preserves a well-defined potential barrier between the source and drain, allowing for precise carrier modulation even at deeply scaled channel lengths. Furthermore, unlike conventional semiconductors that suffer from surface states and dangling bonds at the semiconductor-dielectric interface, 2D vdW materials exhibit pristine surfaces with van der Waals bonded layers, eliminating trap-induced Coulombic scattering. This absence of interface trap states reduces carrier scattering at the semiconductor-dielectric interface, facilitating ballistic or quasi-ballistic charge transport. As the gate length  $(L_{\sigma})$  is reduced below 5 nm, the simultaneous reduction in channel length and body thickness imposes severe constraints on the electrostatic integrity and carrier transport of Si-based transistors. Although bulk silicon possesses an intrinsic electron mobility of approximately 1000 cm<sup>2</sup>/Vs, this value deteriorates drastically in ultra-scaled geometries due to pronounced short-channel effects (SCEs) such as drain-induced barrier lowering (DIBL) and direct source-to-drain tunneling, ultimately making it increasingly difficult for silicon to sustain reliable switching performance at such dimensions. In contrast, atomically thin 2D materials, when implemented in lateral device architectures [142, 143], enable aggressive channel length scaling down to the sub-1 nm regime while maintaining strong gate control and suppressing SCEs. Wu et al. [143], demonstrate sub-1 nm channel length transistors ("side-wall transistors") based on 2D lateral heterostructures, exhibiting a subthreshold swing as low as 117 mV dec<sup>-1</sup>, and an  $I_{\text{on}}/I_{\text{off}}$  ratio of ~ 10<sup>5</sup>, all on a 2-inch wafer platform. These findings underscore the unique potential of 2D semiconductors in extending Moore's law beyond the physical limits of silicon. Consequently, 2D FETs demonstrate superior electrostatic integrity, low off-state leakage, and enhanced energy efficiency, making them promising candidates for further sub-10 nm transistor technologies.

Among the diverse class of 2D van der Waals semiconductors, indium selenide (InSe) has emerged as a promising 2D semiconductor for high-performance FETs due to intrinsically high carrier mobility, tunable bandgap, and strong gate modulation capabilities. Despite its advantageous electrical properties, InSe suffers from air instability, which leads to oxidation and defect formation, and contact resistance ultimately degrading device performance. To

overcome these limitations, surface charge transfer doping (SCTD) approach using an indium (In) encapsulation layer was developed, significantly enhancing both the electrical performance and long-term operational stability in InSe FETs [144]. As illustrated in Fig. 5c, mechanically exfoliated InSe nanosheets (10–13 layers, ~9.21 nm thickness) were transferred onto Si/SiO<sub>2</sub> (300 nm) substrates in a backgate FET configuration. The In-encapsulated (w/In) InSe FET exhibits a dramatic enhancement in drain current  $(I_{ds})$ and gate tunability, eliminating the severe current suppression observed in unencapsulated (w/o In) devices (Fig. 5d). This confirms SCTD-driven n-type doping, which reduces the Schottky barrier at the source/drain contacts and facilitates seamless carrier injection. Further evidence of contact resistance reduction is seen in Fig. 5e, where the output characteristics  $(I_{ds}-V_{ds})$  reveal a near-ohmic behavior at  $V_{bg}$  $=\pm$  80 V, ensuring efficient charge transport owing to a lowered Schottky barrier at metal-semiconductor interfaces. Figure 5f exhibits temperature-dependent field-effect mobility  $(\mu_0)$ , which peaks at an impressive ~ 9100 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at 80 K. This increase in mobility at low temperatures is largely due to the suppression of phonon scattering, which dominates at higher temperatures. For 2D semiconductors, longterm stability is just as critical as high performance. The hysteresis-free transfer curves in Fig. 5g demonstrate that In encapsulation prevents charge trapping, ensuring consistent Vth and  $I_{\rm ds}$  over 50 days of operation. Raman spectroscopy (Inset, Fig. 5g) confirms minimal structural degradation, underscoring the effectiveness of In encapsulation in suppressing environmental-induced defects.

While most 2D vdW semiconductors inherently exhibit n-type behavior, certain materials, such as black phosphorus (BP) and tungsten diselenides (WSe<sub>2</sub>), have been identified as promising p-type or ambipolar candidates. Achieving stable and efficient p-type conduction in 2D transistors is essential for realizing complementary logic circuits, optoelectronic devices, and neuromorphic computing architectures. The following studies illustrate how band structure engineering, doping, and solution-processing strategies are transforming 2D FETs beyond traditional n type transport. BP [145, 146] has emerged as a promising candidate for next-generation nanoelectronics due to its intrinsic p type transport, high hole mobility, and layer-dependent bandgap tunability, distinguishing it from conventional n type-dominated 2D TMDs. Unlike TMDs, which require chemical doping or electrostatic gating to achieve p type

conduction, BP naturally supports hole transport, making it an essential material for all-2D complementary logic circuits. Furthermore, its tunable bandgap, which ranges from 2.0 eV in monolayer BP (black phosphorene) to ~0.3 eV in bulk, enables precise control over charge carrier dynamics, facilitating its integration into high-performance transistors, near-infrared optoelectronics, and logic circuits [147]. The electronic transport properties of BP exhibit a non-monotonic dependence on thickness, dictated by the interplay of bandgap evolution, electrostatic gate efficiency, and charge carrier scattering mechanisms. In the monolayer limit, BP retains a large direct bandgap (~2.0 eV) due to quantum confinement effects, which enhances p-type conduction by stabilizing the valence band edge while suppressing thermally excited electron transport. However, several limitations arise in this ultra-thin regime: 1) Strong quantum confinement and surface effects. The quantum confinement-induced bandgap widening increases the hole effective mass, limiting carrier mobility. Additionally, the strong influence of surface interactions makes monolayer BP highly sensitive to environmental conditions and dielectric effects, posing challenges for device stability and performance. 2) Coulombic scattering and interface roughness effects. As monolayer BP lacks sufficient charge screening, it is highly susceptible to charged impurity scattering, particularly from the underlying dielectric. This leads to mobility degradation despite strong electrostatic gate modulation. While monolayer BP provides excellent gate tunability, its mobility remains constrained by strong carrier-impurity interactions and surface scattering. Notably, the monolayer BP is more air-sensitive at the monolayer level than thicker layers. As BP thickness increases, its bandgap gradually narrows to ~0.6-0.7 eV at ~10 nm, significantly enhancing charge carrier mobility. This thickness range offers optimal transport characteristics, as demonstrated by BP FETs fabricated using ~ 10-nm-thick mechanically exfoliated BP [148]. Few-layer BP FETs exhibit one of the highest hole mobilities (~1000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) at room temperature among p-type 2D semiconductors, significantly surpassing most TMD-based transistors. The additional layers provide better charge screening, reducing Coulombic impurity scattering and improving transport efficiency. The reduced bandgap in few-layer BP results in stronger band dispersion, lowering the hole effective mass and facilitating efficient charge transport. At ~ 10 nm thickness, BP maintains strong gate control while minimizing interfacial disorder, achieving an optimal balance between mobility, bandgap tunability, and electrostatic gating efficiency.

In another study, they demonstrated the fabrication of wafer-scale arrays of molybdenum disulfide (MoS<sub>2</sub>)-based transistors through a commercial slot-die printing process. Utilizing tailored inks of MoS2 nanosheets and sodiumembedded alumina (SEA), we achieve precise deposition of the semiconductor and gate dielectric layers, respectively. The resulting transistors achieve remarkable charge carrier mobilities of 80.0 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in FET measurements and 132.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in Hall measurements at room temperature, with uniformity across the wafer. The high mobility observed in the MoS<sub>2</sub>-on-SEA devices is primarily attributed to the SEA dielectric layer, which promotes band-like charge carrier transport through the well-percolated MoS<sub>2</sub> thin-film networks. The SEA layer's high dielectric constant enables efficient electron mobility by fostering van der Waals sheetto-sheet contacts with energetically flat electronic properties, enhancing uniformity across the five-inch wafers. Notably, the high-K dielectric properties of SEA are advantageous for solution-processed MoS<sub>2</sub> thin films, comparable to those of hafnium oxide (HfO<sub>2</sub>) or aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), which are typically used to enhance field-effect mobility. Additionally, they successfully integrate these transistors into logic circuits such as NOT, NAND, NOR, and SRAM, demonstrating a viable pathway for large-area, solution-processed 2D electronics. This approach provides a promising route to high-performance, flexible electronics based on 2D materials at commercial scales [141].

To enhance the electrical performance and stability of 2D materials, chemical doping and functionalization are widely utilized, as their effects are particularly impactful in 2D systems. In MoS<sub>2</sub> transistors, for instance, TFSI (trifluoromethanesulfonimide) chemical treatment has demonstrated substantial improvements, with electron mobility increasing from 4.7 to 18.9 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and a fivefold enhancement in subthreshold swing. Previous studies suggest that TFSI molecules passivate sulfur vacancies on the basal plane of MoS<sub>2</sub> nanosheets, which function as carrier trapping sites, thereby reducing the density of charge traps. Furthermore, TFSI acts as a Lewis acid, effectively lowering the charge density of MoS<sub>2</sub> by withdrawing electrons. This reduction in charge density significantly lowers the off-current, thus maximizing the  $I_{on}$ - $I_{off}$  ratio and enhancing device performance [132, 141]. Building on this, T. Zou et al. present an

69

effective doping strategy using bromine (Br<sub>2</sub>) to enhance the hole mobility and operational stability in p-type transistors based on 2D WSe<sub>2</sub>. While TFSI treatment has shown significant performance gains for n-type MoS2 by passivating sulfur vacancies and lowering charge density, Br<sub>2</sub> doping offers a similarly transformative effect for p-type WSe<sub>2</sub> transistors. Specifically, Br<sub>2</sub> doping increases the field-effect hole mobility from  $\sim 0.004$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (undoped) to 27  ${\rm cm^2~V^{-1}~s^{-1}}$  and achieves an  $I_{\rm on}/I_{\rm off}$  current ratio exceeding 10<sup>7</sup>, with excellent stability under repeated cycling, bias stress, and switching conditions. Density functional theory (DFT) calculations reveal that Br<sub>2</sub> molecules adsorb onto the WSe<sub>2</sub> surface, covering up to 25% and creating shallow acceptor states near the valence band maximum. The doping reduces contact resistance and enhances charge transport by lowering the Schottky barrier at metal contacts to ~80 meV, compared to the 1 eV barrier typically seen in undoped WSe2. This allows efficient hole injections, as demonstrated by temperature-dependent measurements, where Br<sub>2</sub> doping achieves low activation energy  $(E_a)$  values (32– 85 meV) across the channel. This improved charge injection and transport are attributed to reduced channel resistance and minimized inter-flake hopping. The enhanced charge injection and transport in Br<sub>2</sub>-doped WSe<sub>2</sub> transistors are primarily due to a substantial reduction in channel resistance and minimized inter-flake hopping. Br<sub>2</sub> has proven to be the most effective p-type dopant of WSe<sub>2</sub>, significantly increasing hole concentration and lowering channel resistance compared to other doping treatments like ultraviolet (UV)-O<sub>3</sub>, HBr, TFSI, and PEDOT treatments. Br<sub>2</sub>'s small molecular size allows it to penetrate inter-flake boundaries and contact regions, facilitating uniform and comprehensive doping across nanoflake films, which overcomes the limitations of conventional molecular dopants typically restricted to surface adsorption [149].

The two-dimensional van der Waals materials, including InSe, BP, molybdenum telluride (MoTe<sub>2</sub>), tin sulfide (SnS<sub>2</sub>), and others, are highly sensitive to air or moisture, necessitating careful handling under inert environments or the use of passivation layers to prevent degradation and maintain their properties for applications. Among these materials, BP stands out due to its high charge carrier mobility, tunable bandgap, and strong anisotropic properties. However, it rapidly degrades in ambient conditions due to its reactivity with oxygen and water, resulting in a substantial loss of electronic performance. To address this instability, covalent

functionalization with aryl diazonium salts has proven to be an effective method for stabilizing BP. This approach forms robust phosphorus-carbon (P-C) bonds that effectively passivate BP, preserving its morphology and preventing degradation for over three weeks in ambient exposure. The chemical functionalization was achieved by immersing few-layer BP (~10 nm thick, prepared by ME) in a solution of 4-nitrobenzene diazonium (4-NBD) tetrafluoroborate salts. The functionalized BP exhibits robust morphology and stable atomic force microscopy (AFM) profiles even after extended air exposure, confirming effective passivation. Note that air-sensitive materials, when exposed to ambient conditions, rapidly form an oxide layer, leading to an increase in thickness and surface roughness. This functionalization also improves the electronic properties of BPbased FETs. Specifically, the p-type doping introduced by aryl diazonium chemistry enhances both the  $I_{or}/I_{off}$  and hole carrier mobility of BP FETs. Higher doping levels achieved through increased aryl diazonium concentration reduce current modulation as BP becomes degenerately doped, while lower concentrations (~1 µM) allow for controlled doping with minimal  $I_{\text{off}}$  increase. The functionalization rate is influenced by the reduction potential of the aryl diazonium substituent, allowing precise control over BP's electronic characteristics. Consequently, aryl diazonium chemistry provides a promising approach for enhancing both the stability and performance of BP-based devices [150].

Figure 5h illustrates the correlation between carrier mobility and channel thickness in 2D van der Waals semiconductors synthesized via various techniques, including ME, LPE, CVD, and MOCVD. The data show that mechanically exfoliated few-layer graphene and InSe achieve the highest mobility, exceeding  $10^4 \, \mathrm{cm}^2 \, \mathrm{V}^{-1} \, \mathrm{s}^{-1}$  at cryogenic temperatures ( $T=4 \, \mathrm{K}, \, 20 \, \mathrm{K}$ ), surpassing theoretical expectations. Ultimately, when precisely engineered, 2D semiconductors have the potential to bridge the gap between high-performance transistor technologies and scalable device manufacturing, facilitating their integration into next-generation electronic and optoelectronic systems.

#### 4.2 Halide Perovskites

Recent advances in HP semiconductors, primarily in optoelectronic applications, have renewed attention in their use for transistors. HPs are emerging as promising semiconductor

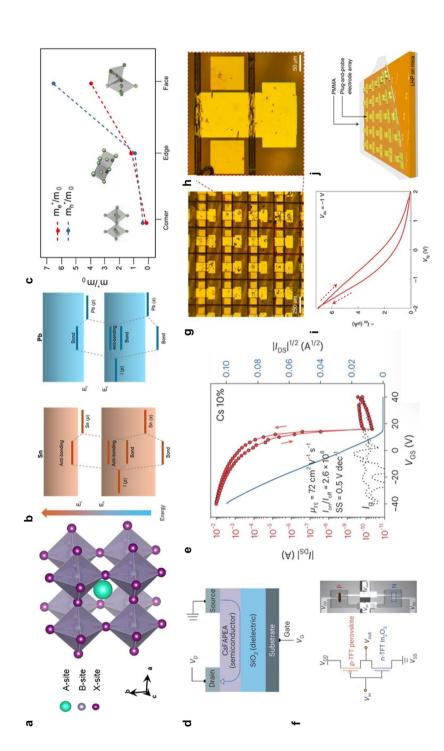

candidates to replace silicon in advanced transistor technologies. Their unique material characteristics, such as lowtemperature processability, defect tolerance, and ambipolar transport, offer fundamental advantages over conventional silicon, which suffers from short-channel effects, high contact resistance, and S.S. limitations in the sub-5 nm regime [161, 162]. Notably, the intrinsic ionic motion in perovskites enables mixed ionic-electronic conduction, allowing for tunable switching behavior and neuromorphic functionalities not achievable in rigid covalent semiconductors like silicon [163]. These attributes, combined with the ability to engineer electronic properties via compositional tuning, position HPs as a compelling platform for next-generation lowpower, high-density, and multi-functional transistors [164]. MHPs are a class of compounds with an ABX<sub>3</sub> crystal structure, where A represents a monovalent organic or inorganic cation, B is a divalent metal cation such as Pb<sup>2+</sup> or Sn<sup>2+</sup>, and X corresponds to a halide anion, including Cl<sup>-</sup>, Br<sup>-</sup>, or I<sup>-</sup>. As illustrated in Fig. 6a, the  $[BX_6]^{4-}$  octahedra form a corner-sharing network within a cubic or tetragonal lattice, while A-site cations occupy the interstitial spaces, stabilizing the structure [165]. These materials exhibit long charge carrier diffusion lengths, high charge mobility, and defect tolerance, making them attractive candidates for transistor applications. Unlike conventional semiconductors, perovskites can be processed at low temperatures, offering a costeffective and scalable alternative to traditional silicon-based thin-film transistors. The electronic properties of HPs are highly sensitive to their synthesis conditions, necessitating controlled processing strategies to ensure device stability, scalability, and performance [166]. The ability to process MHPs at low temperatures offers a significant advantage over conventional polycrystalline silicon thin-film transistors, which require thermal processing above 400 °C. Two primary deposition strategies exist for MHP thin films: onestep deposition and two-step deposition [167].

In one-step deposition, all precursor components such as MAI and PbI<sub>2</sub> are co-deposited onto a substrate via solution-processing or vapor-phase methods. This approach is attractive due to its simplicity and rapid film formation, making it suitable for commercial production. However, rapid crystallization often leads to poor film morphology and high defect densities. To address these issues, anti-solvent engineering is employed, where a non-coordinating solvent is introduced during spin coating to promote uniform nucleation and suppress defect formation [168]. Additionally, dual-source or

single-source evaporation techniques enable vapor-phase deposition of perovskite precursors under vacuum, forming high-purity thin films with excellent crystallinity, albeit at the cost of increased fabrication complexity and lower deposition rates [169].

In two-step deposition, precursor materials are sequentially deposited. Typically, a metal halide such as PbI<sub>2</sub> is first deposited as a thin film, followed by exposure to an organic halide vapor or solution to induce perovskite conversion. This method allows for better control over crystallinity, thickness, and uniformity, albeit at the expense of increased processing steps and longer fabrication times. Furthermore, precise interface engineering is crucial to minimize interlayer defects that could degrade transistor performance. Solution-based processing techniques, such as spin coating, blade coating, and inkjet printing, enable large-area deposition with cost-effective manufacturing. However, residual solvents can lead to performance degradation, requiring post-deposition annealing and additive engineering to optimize film morphology and electronic properties. While vacuum-based techniques offer superior stability, they require further optimization for scalable manufacturing [158].

The charge transport characteristics of MHPs are strongly influenced by their chemical composition, phase stability, and structural connectivity [166]. The B-site cation plays a crucial role in determining the semiconductor type, with Pb-based perovskites typically exhibiting ambipolar transport behavior, whereas Sn-based perovskites strongly favor p-type conduction due to the presence of Sn vacancies (Fig. 6b) [170]. Sn-based perovskites offer higher hole mobility but suffer from excessive carrier concentrations, making field-effect modulation challenging. In contrast, Pbbased perovskites benefit from stronger spin-orbit coupling, resulting in enhanced band dispersion and tunable transport properties [162, 171]. In addition to composition, octahedral connectivity significantly impacts charge mobility. Cornersharing octahedral networks minimize carrier effective mass, leading to superior charge transport compared to edge- or face-sharing configurations (Fig. 6c) [172]. This structural advantage makes corner-sharing perovskites highly desirable for high-mobility FETs, where isotropic charge transport is required [161].

Despite their promising properties, MHPs face stability challenges related to ion migration. Halide ion diffusion leads to hysteresis in electrical characteristics and  $V_{\rm th}$  shifts in FETs. Additive engineering offers a practical approach

69

Nano-Micro Lett. (2026) 18:69 Page 17 of 59 69

Fig. 6 Halide perovskite transistors. a Crystal structure of halide perovskites. b Band positions of Sn- and Pb-based halide perovskites. c Carrier effective mass of halide perovskites as a function of increasing the octahedron connectivity. Reproduced with permission from [181]. Copyright 2022 American Chemical Society. d Schematic structure of a Sn-based perovskite transistor. e Transfer characteristics of a CsFAPEA-based transistor. f Structural scheme and optical image of the inverter. Reproduced with permission from [16]. CC BY 4.0. g Optical microscopy image and h magnified view of a selected region showing the fabricated top-gated perovskite transistor array. I Transfer curve of a perovskite transistor. J Schematic illustration of a plug-and-probe electrode array on a mica substrate. Reproduced with permission from [179]. Copyright 2022, Springer nature

to suppressing defect formation. For instance, SnF2 additives mitigate Sn vacancy formation, improving p-type transport stability, while RbCsFAMA cation engineering has been shown to minimize hysteresis in Pb-based perovskites [132, 173]. Additionally, halide substitution including Br or Cl for I promotes enhanced crystallization and passivates iodine vacancies, further reducing defect densities. Interfacial engineering is equally critical in optimizing MHP transistor performance. The semiconductor/dielectric and semiconductor/electrode interfaces strongly influence charge injection, mobility, and hysteresis behavior. Using MoO<sub>x</sub> hole injection layers has been demonstrated to enhance hole mobility in 2D (PEA)<sub>2</sub>SnI<sub>4</sub> transistors, while employing high-K dielectrics like HfO<sub>2</sub> has enabled the realization of hysteresis-free perovskite transistors [174]. Addressing interfacial stability remains a key challenge for the practical deployment of MHP-based electronics.

69

HP-based transistors were first demonstrated in 1999 by IBM using (PEA)<sub>2</sub>SnI<sub>4</sub> as a p-type TFT channel material [175]. However, material instability hindered further development until 2014, when renewed interest emerged with the demonstration of MAPbI3-based transistors and self-doped ambipolar transport characteristics [176, 177]. Recently, high-performance CsSnI<sub>3</sub>-based TFTs have achieved  $\mu_h$ exceeding 50 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and  $I_{on}/I_{off}$  of 10<sup>8</sup>, surpassing conventional amorphous silicon (a-Si) and oxide semiconductors in charge transport efficiency [166]. Furthermore, Zhu et al. demonstrated a high-performance transistor based on A-site engineering (Fig. 6d). The device shows an exceptionally high hole mobility of 70 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and an  $I_{on}/I_{off}$  of 10<sup>8</sup> (Fig. 6e) [16]. The optimization of the Cs molar ratio was key to fabricating high-quality perovskite films, enabling the successful integration of NAND and NOR logic gates (Fig. 6f) [16]. These advancements highlight the potential of MHP transistors not only for logic applications but also for low-power electronics. Beyond their conventional use in FET applications, MHPs have demonstrated significant potential for neuromorphic computing due to their unique mixed ion-electron conduction properties [163]. Ion migration in perovskites mimics synaptic plasticity, where halide ions and metal vacancies act as dynamic charge trapping sites, enabling multi-level resistive states for hardware-based AI learning. Unlike conventional resistive random-access memory (RRAM) devices, 3-terminal neuromorphic transistors based on perovskites allow for decoupled signal processing and weight updating, enhancing learning stability and energy efficiency. Jeong et al. demonstrated a CsPbBr<sub>3</sub> transistor with a ferroelectric gate that successfully emulated synaptic behavior, offering a promising path toward hardware-integrated artificial intelligence systems [178].

Given their tunable band structures and ionic transport characteristics, perovskites also present opportunities for hybrid integration with existing semiconductor technologies. Combining MHPs with 2D materials such as MoS<sub>2</sub> and WS<sub>2</sub> enables high-performance, energy-efficient neuromorphic computing architectures, while plug-and-probe integration techniques facilitate CMOS-compatible device fabrication (Fig. 6g, h) [179]. This approach involves the simultaneous vdW integration of high-K dielectrics and contacts in a single step. They fabricated top-gated CsPbBr<sub>3</sub> transistors showing low operating voltage (Fig. 6i) and the transistor array using the vdW plug-and-probe method offering a reliable path toward scalable fabrications (Fig. 6j). Moreover, heterostructures integrating perovskites with TMDs have demonstrated bio-inspired optical adaptation, paving the way for intelligent image sensors and AI-driven vision systems [180].

HPs exhibit unique advantages for next-generation semiconductor applications, bridging the gap between highperformance electronic materials and scalable, low-cost processing techniques. Advances in synthesis control, interfacial engineering, and hybrid integration have significantly improved material stability and device performance, making them viable candidates for low-power computing, neuromorphic devices, and flexible electronics. While longterm stability and CMOS compatibility remain critical challenges, ongoing innovations in material design and device fabrication hold great promise for realizing perovskite-based electronics in future semiconductor technologies.

### 4.3 Mott Insulators

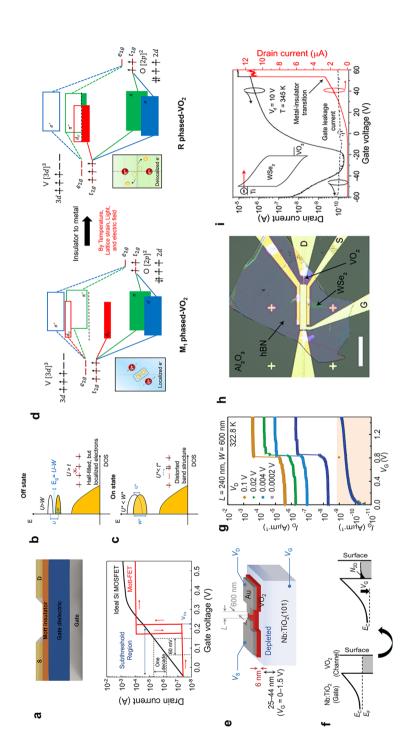

For ultra-fast switching and low-power operation in transistors, Mott insulators have emerged as promising semiconductor candidates. Despite being termed "insulators," these materials exhibit unique electronic properties in transistors due to electron correlation effects induced by external stimuli such as gate voltage, light exposure, temperature, or pressure [15]. This correlation-driven phenomenon enables metal—insulator transition (MIT) behavior in Mott insulators, leading to high resistivity contrast and significant

variations in charge density. The dramatic modulation of charge density via bandgap formation/collapse has been actively explored in semiconductor channels, giving rise to a new class of devices known as Mott transistors. In contrast to silicon, where scaling below 5 nm is hindered by short-channel effects and fundamental thermal limits on subthreshold swing, Mott systems offer steep-slope switching (sub-10 mV dec<sup>-1</sup>) and retain robust electrostatic integrity even at atomic dimensions [182]. Their high intrinsic carrier density, coupled with negligible Thomas-Fermi screening, facilitates gate coupling at nanometric thicknesses without compromising  $I_{on}/I_{off}$  ratios or mobility [183]. These features collectively position Mott insulators as compelling candidates for beyond-CMOS logic, where ultra-low-power operation, aggressive dimensional scaling, and neuromorphic functionality converge. Various Mott insulators, including NiO [184], NbO<sub>2</sub> [185], ternary chalcogenide compounds [182], and VO<sub>2</sub>, exhibit MIT behavior. However, this review will focus specifically on VO<sub>2</sub>-based Mott transistors. As a representative Mott insulator, VO2 undergoes an MIT in which the insulating monoclinic  $(M_1)$  phase transforms into the metallic rutile (R) phase when subjected to temperatures above 68 °C [186] or high surface charge densities exceeding 10<sup>15</sup> cm<sup>-2</sup> under a strong electrostatic field [187].

Beyond the conventional MIT in VO<sub>2</sub>, its ability to achieve ultra-fast switching within just a few picoseconds [188] and operate with extremely low writing energies below 100 fJ [168] makes VO<sub>2</sub>-based transistors highly promising for low-power logic applications. Additionally, VO<sub>2</sub> offers a pathway to overcoming the scaling limits of conventional semiconductors due to its negligible Thomas-Fermi screening effect [15]. Notably, even at dimensions below 10 nm, electron delocalization in VO<sub>2</sub> preserves high conductivity comparable to a bulk film [187], making it an excellent candidate for ultra-scaled semiconductor devices. As depicted in Fig. 7a, the typical switching behavior of Mott transistor is introduced. This performance is distinctly different from that of conventional FET. By inducing much lower S.S. value that overcomes the typical thermionic limit (60 mV dec<sup>-1</sup>), the abrupt switching becomes possible. Shukla et al. reported a super steep-slope transistor in which VO2 is connected to the drain electrode of an InGaAs quantum well FinFET [189]. All these examples of fast switching in the case of VO<sub>2</sub> transistors are attributed to the abrupt electron delocalization in the channel, allowing MIT behavior to be observed during switching. Figure 7b, c provides further insight into this switching mechanism using density of states (DOS) diagram. Unlike conventional FETs, where channel formation occurs through thermal excitation of carriers by an external gate field, Mott FETs undergo band structure modifications that facilitate electron delocalization. Since the electronic state, in other words band structure, transitions along with the structural phase change (Fig. 7d), this process is inherently rapid and allows for a lower *V*th.

Leveraging the unique and intriguing electronic phenomena in VO<sub>2</sub>, various types of transistors have been developed. Yajima et al. reported an unconventional transistor configuration in which a depletion region between Nb-doped TiO<sub>2</sub> and VO<sub>2</sub> served as a virtual gate dielectric (Fig. 7e) [190]. The VO<sub>2</sub> layer was epitaxially grown on an Nb-doped TiO<sub>2</sub> substrate with a precisely controlled thickness of 6 nm. As shown in Fig. 7f, the interface between VO<sub>2</sub> channel and the substrate formed a depletion region extending several tens of nanometers. This depletion layer acted as an insulating barrier between the gate and the channel. When a positive gate voltage was applied to the substrate, the depletion layer expanded, attracting a high concentration of electrons. This substantial electron accumulation induced a metallic state in VO<sub>2</sub>, enabling low-power isothermal switching at an extremely low  $V_{\rm ds}$  (0.004 V) while achieving an  $I_{\rm on}/I_{\rm off}$  ratio of 10<sup>3</sup> (Fig. 7g). VO<sub>2</sub> has also been integrated into 2D FET as drain electrode. Yamamoto et al. demonstrated a device utilizing a TMD 2D material, WSe2, with an hBN gate dielectric, where a VO<sub>2</sub> nanowire was employed as the drain electrode (Fig. 7h). Notably, charge carriers in 2D channel were ambipolarly modulated and exhibited abrupt magnification, resulting in an  $I_{on}/I_{off}$  current ratio of  $10^3$  and S.S. of 60 mV dec<sup>-1</sup> (Fig. 7i). This current amplification was attributed to the MIT behavior in VO<sub>2</sub>, induced by gate-mediated self-heating. As illustrated in these studies, VO<sub>2</sub>, whether utilized as a semiconductor or a drain electrode, facilitates ultra-fast switching enabled by gate-induced MIT behavior. This gate tunability in VO<sub>2</sub>-based transistors highlights their potential as promising candidates for low-power transistor applications.

# 4.4 Amorphous Oxide Materials

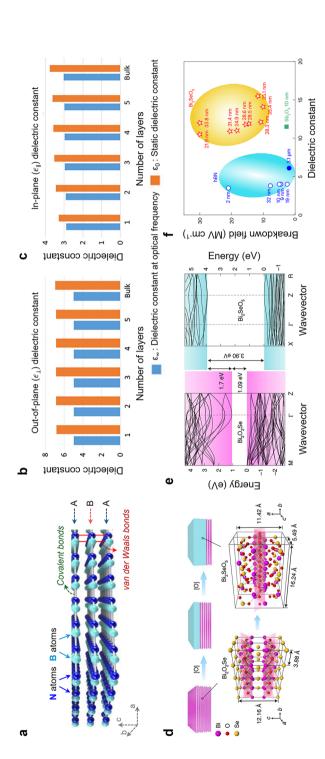

AOS materials offer distinct advantages over conventional silicon as transistor channel materials, particularly in the era of device scaling and heterogeneous integration. AOS

69 Page 20 of 59 Nano-Micro Lett. (2026) 18:69

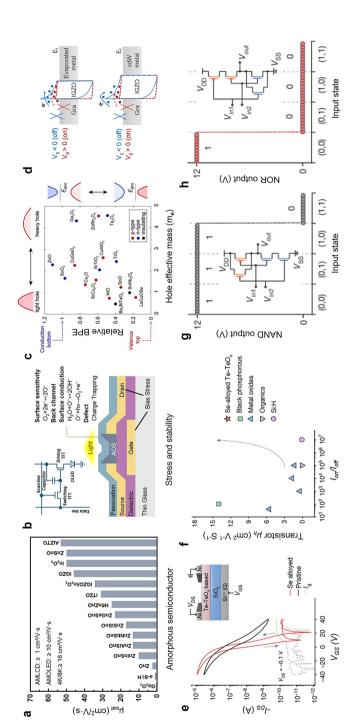

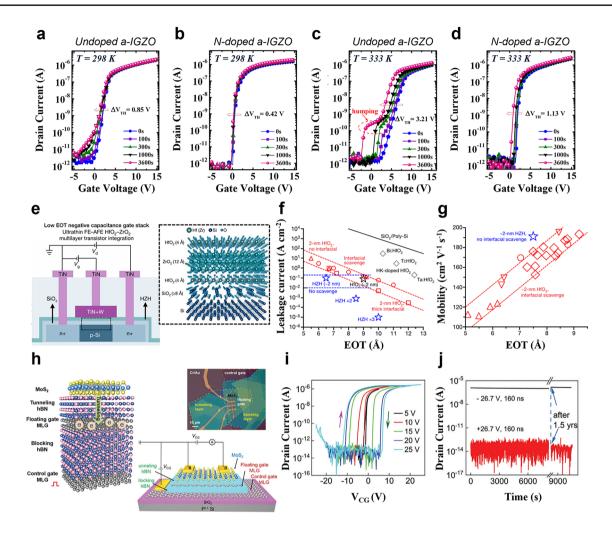

Fig. 7 Mott transistor. a Schematic illustration of a typical Mott transistor with a bottom-gate top-contact (BGTC) structure, demonstrating abrupt switching behavior with a small S.S. value. The electronic structure of the Mott insulator is depicted in the b off state and c on state. Reproduced with permission [15], Copyright 2024, Wiley-VCH GmbH. d Changes in the band structure of VO<sub>2</sub> as it transits from the M<sub>1</sub> insulating phase to the R metallic phase under various perturbations, including temperature, lattice strain, light, and electric field. e A Three-terminal VO<sub>2</sub> transistor using a Nb-TiO<sub>2</sub> gate electrode. f Band diagram of the VO<sub>2</sub>/Nb-TiO<sub>2</sub> contact during the operation of the device shown in Fig. 7e under gate voltage application. g Transfer characteristics at various drain voltages, ranging from 0.0002 to 0.1 V, measured at 322.8 K. Reproduced with permission [190], Copyright 2023, Nature Publishing Group. h Multilayer WSe2 transistor with a VO2 contact electrode as the drain and hBN as gate dielectric. i Transfer curve of the device in Fig. 7 h measured at 345 K, along with the gate leakage current (Ig). Reproduced with permission [191], Copyright 2019, American Chemical Society

materials exhibit intrinsically low leakage due to their wide bandgap, high carrier mobility even in amorphous phases, and superior compatibility with low-temperature, large-area fabrication techniques, unlike silicon, which suffers from increasing short-channel effects, high-leakage currents, and process-induced variability at nanometer dimensions [192]. Furthermore, their grain boundary-free structure ensures electrical uniformity, and dielectric interfaces enable reliable switching characteristics [193]. AOS materials have been extensively studied as a replacement for hydrogenated amorphous silicon (a-Si:H) in flat-panel display backplanes since Nomura et al. first demonstrated a flexible TFT using amorphous IGZO (a-IGZO) in 2004 [194]. The key performance metrics of AOS TFTs, including  $\mu_0$ , Vth, and S.S., are influenced by device structure, fabrication process, material composition, gate dielectrics, and contact metal properties. Given their role in fast switching applications, high  $\mu_{EE}$ , a Vth near zero, and a low S.S. are critical for optimal performance [195] As shown in Fig. 8a, a-Si:H TFTs have a low electron mobility ( $\mu_e$ ) of approximately 1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, whereas n-type AOS materials exhibit significantly higher mobility, offering superior electrical performance. In particular, a-IGZO's high mobility makes it a key candidate for display backplanes. The growing demand for 4 K and 8 K resolution displays necessitates AOS-based switching matrix TFTs with enhanced mobility [196]. Figure 8a indicates that a minimum mobility of 16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> is generally required for 4 K displays, highlighting AOS materials suitable for industrial adoption. Beyond high mobility, AOS supports low-temperature, large-area processing, making it well suited for flexible displays and wearable electronics, key applications for next-generation device technologies [192, 193, 195, 197–200].

AOS TFTs used in active matrix organic light emitting diode (AMOLED) and active matrix liquid crystal display (AMLCD) applications can suffer from instability due to gate bias stress, illumination, and environmental factors (Fig. 8b) [201, 202]. These reliability issues can be categorized into five key factors affecting long-term performance. The first factor is bias stress, which occurs due to charge trapping under prolonged gate voltage. Positive bias stress (PBS) causes electron trapping in the gate dielectric or at the channel/dielectric interface, shifting Vth positively. Conversely, negative bias stress (NBS) leads to hole trapping or defect state formation, decreasing Vth, making voltage stability a major challenge for display-driving devices.